# 高速数字电路系统中的信号完整性工程

译自 1997 high-performance system Design Conference 原著作者 Donald Telian

- 摘 要:与一门成熟的学科不同,信号完整性工程的方法和实践还都没有很好的 定义。但勿庸置疑,保证电气性能的完整是高速数字电路设计的又一 难题。本文针对硬件设计流程总结出信号完整性工程师应该表现出的 七方面作用,阐述了如何正确应用信号完整性的理论、工具和方法去 建立新规则,解决生产中的问题。本文从成功实践中总结了一些规则 和技巧以飧读者。

- 作者简介: Donald Telian 是 Cadence Design-systems' Spectrum Scrvices 的 首席顾问,主要任务在于解决 Cadence 世界各地的用户中在高速电路 设计中遇到的难题。

#### 正 文:

本文将阐述信号完整性工程如何成为当今高速电路设计系统中的重要组成部分。我们首先定义"高速"为 25MHZ 以上的数字信号,而且不是 IC 内部的数字信号。

本文简要讨论在过去 10-15 年中系统设计的变化,目的是说明:这些变化导致了一种新的工程师的产生;信号完整性工程师。

本文将说明: 在硬件设计的整个流程中,信号完整性工程师的参与都是必要的,本文将参与过程总结"信号完整性工程师的7方面作用。"

(1) 数字系统设计有三个初始的方面: 机械的(Mechanical),逻辑的(Logical)和电气的(Electrical),当机械和逻辑方面的内容在不断变化时,电气部分也在进行着有趣的改变。

电气设计的改变源于电路开关速度的提高。在低速系统中,如工作在 1MHz 时钟下,信号在周期的 95%的时间内是保持不变的,因此电气参数大多描述静态,如 V\_in, L\_o1 等。而今在 66M 系统中的信号用周期的 1/3 来翻转。这些信号常常还未到一个"静止"状态,便被要求翻转。因此新的数据形式象 IBIS 模型、规迹(RAIL)文件等,和鲁棒(robust)而复杂的仿真工具便出现了,用来描述这些电气表现。

然而,虽然这些技术是奏效的,它们在工业界的应用和判决标准还未达到统一的,一位信号完整性工程小组的组长如是说:工程倾向于完善定义的稳定的任务和处理方式,而现在信号完整性工程的实践者却在用不充足的数据、不稳定的

处理方法以期产生可接受的结果。

(5) 因此我们要问,什么时候才能做到有充分的数据,良好的工具和正确的处理方法,来保证信号完整性呢?现在很难回答这个问题。不过我们可从保证设计机械完整性和逻辑完整性上的发展中得到些启示。

早期 PCB 设计完全靠手工测量器件之间、走线之间距离的错误,用高亮方式标记,然后人工修改。后来,手工测量消失了,软件具备了自动测量间距的功能,并自动标注错误。这就做到了机械完整性。逻辑完整性也走了相似的过程,在PCB 和 IC 设计中都是如此。

虽然电气完整性还未达到这一步。但可肯定,未来几年中,信号完整性将成为一个明确的任务。现在有一批专家级人物正工作在这个领域,成为最早的信号 完整性工程师。

#### (6) 介绍:信号完整性工程师

在工业界信号完整性工程师的作用在不断增加,总得来说:这种工程师不断将数据通过仿真工具转换为可实现的设计。他的工作是在设计过程和数据类型还未成熟的时候,找到工艺(craft)方案。

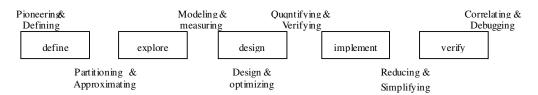

- (7) 本文将信号完整性工程师的作用总结成7条,它们是:

- 1) pioneering and defining 研究 定义

- 2) Partitioning 和 Approximating 分类 总结

- 3) Modeling and Measuring 建模 测量

- 4) Designing and optimizing 设计 优化

- 5) Quantifying and verifying 量化 验证

- 6) Reducing and simplifying 减少 简化

- 7) Correlating and Debugging 联系和调试 这7条分别偏重于硬件设计流程的不同方面。

#### (8) 硬件设计流程

Define new project 定义→explore option 研讨→Design—schematic 设计→implement layout/fab 实现→Verify proto 验证

在将"7个作用"映射到硬件设计流程之前,我们先看看硬件设计流程有哪

些部分。一个产品首先要明确定义它的功能是什么。往下便是分析用到的技术和不同的实现方式。在设计阶段,各种选择经过认真组织和分析,使产品达到可物理实现的阶段。一旦产品定型并经过验证,它便可以生产了。

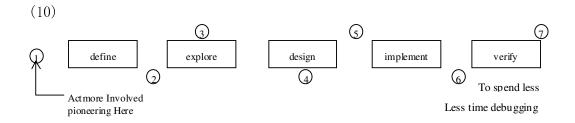

(9)

一个有效的信号完整性工程必须贯穿整个设计流程,不仅在保证设计功能实现(implement)时起作用,在产品定义(define)阶段,它同样起作用。例如:PCI卡上必须有宽带数据交换能力。这便是信号完整性工程师的功劳,他们的研究性工作将商用总线信令的速率从8MHZ 提到33(后66)MHZ。

继续看 PCI 那个例子。如果不能深入了解可靠的信号翻转所需的条件,开发者将在调试阶段用掉更多的时间。甚至, PCI 卡根本不能正常工作。

因此必须指出:信号完整性工程师应该努力将他的技术用到产品设计前期,提高产品可靠性,使高速产品能早日推向市场!

现在遇到的阻力是,很多人依然认为信号完整性的工作是经验性的分析工作,实际上用调试的方法来完善硬件设计是解决问题的下下之策,调试就必须加探针,在当今器件密度越来越大的情况下变得日益困难,使这种经验性的分析越发冗长和令人生厌。

(11) 但是我们必须指出"研究(Pioneering)"的机会通常较少。当一项技术需要从研究到验证七类工作时,你必须有与其他人、其他组织或甚至公司更好的合作能力,才能在硬件设计流程较前的阶段中得到一些机会。

例如:一般调试 PCB 上一个噪声问题用不着与很多人合作,这种机会也是很普遍的,可是,研究却需要不同组织之间精诚合作才能实现一点儿新的思想。

- (12) 在深入讨论 7条作用之前, 先看看对信号完整性工程师的作用的诠释

- 1) 信号完整性工程师的工作是给项目组的工作增添价值(add value)。就象一名交通警察,他的工作就是使众人缓行,避免事故。

- 2) 信号完整性工程师必须能清楚地沟通,他应能用全面的技术通过生动的 3 维模型表达自己工作的价值。很多工程师在演讲中却仅仅让听众迷惑,这是要坚决避免的。

- 3) 仅有工具不能解决问题,一个有工具的傻瓜仍是傻瓜,仿真运行了不等于工作完成了。你要清楚: what it means! 只有给仿真结果以合理的解释,才算实现了仿真的价值,仿真是手段而不是结果。

- 一个资深信号完整性工程师这样说道:我曾与一伙被称为信号完整性领域中 专家级的人物共事,其中有几个家伙拘泥细节,结果收获甚微。这些"科学家" 什么都要研究一番,细致到仿真的第n级精度,却总不能及时得到答案。

- 4) 在任何情况下,有数据总比没有强。当没有恰当模型时,数据太多会束缚手脚,必要时做几个假设来推进研究。

- 5) 及时行动。当你看到了工作不正常的情况马上处理它,事后再说:我早说过,反而说明你没有及时解决问题的能力。

- (13) 为深入解释这 7 条作用,我们先从第七条"调试"看起,因为大多数工程师就是以调试中认识信号完整性工程的。很不幸的是,一些设计公司毫无远见,至今没在设计前期开展足够的分析工作,有可能是他们并不懂高速电路的一些附加效应,或者他们虽然有所感悟但没有更好的办法解决问题。

虽然调试可以积累有价值的经验,但一些常见的问题却没有足够的仪器和技术来调试。对许多噪声毛刺需要 2GHZ 带宽示波器,要仔细安置探针才能观察得到。一位项目经理讲到:调试时,工程师必须对测量系统、控针位置等倍加关注。一点微小的失误便会得到错误的结论。

现在,虽然好仪器可能得到,人们却害怕了示波器。人们会选择逻辑分析仪而扔掉示波器。

一个好办法是主动发现问题。做一个测试计划,分析关键而危险的信号,将 探针对信号做个短暂接触,仅仅检查前面 14 个周期波形。

还有一个办法是在板级仿真器中建一个虚拟的 PCB,设好仿真环境,用仿真解决实验室遇到的问题。

(14) 仿真器的仿真波形是实际测试很好的参考。现在,大多数商用仿真器都有足够准确度。仿真结果与实测的不一致往往源于模型太差,这时必须用准确测试来修正模型。

IBIS 模型的修正方式最简单的。一但模型得到修正,它将在下一次设计中解决问题。

(15)

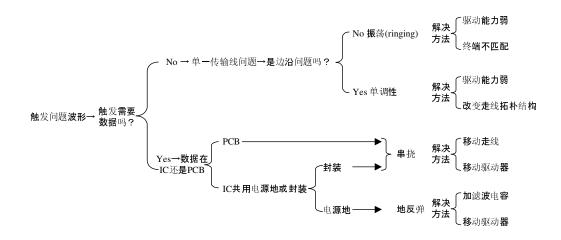

我们凭这幅图可以尽快找到问题原因,信号的不完整有四种表现形式:

地反弹、串扰、单调性和振荡。所有这些失败模式都导致信号采样或时序上 的错误。

首先,我们必须抓住问题波形,这个问题常常并不复杂,用逻辑分析仪就能 奏效,如果用示波器的话,必须在不同条件下观察波形以决定失败模式是否依赖 数据变化。

其次比较困难的是决定引起问题的数据与一个集成电路关系的大小,以此可区分开是 PCB 上的串扰还是 IC 内部串挠。还有 IC 中共用同一电源管脚的总线在一起反转时,在地管脚上因电流过大先造成地管脚电位升高,称为地反弹。

单一传输线问题较简单,对失败波形要反复观察。这些失败波形包括波形边缘不单调、波形振荡等,它们会引起数据判别错误。

(16) 减少和简化(reducing and eionplifying)这个作用的含义一目了然。即是通过分析减少 PCB 层数,去掉不必要的器件,简化终端匹配的器件。

在要设有仿真的时候,很多工程师凭借一些经验规则,往往在设计中加了很 多不必要的器件,许多时候分析表明许多的终端匹配其实是不必要的。

减少器件在物料和生产中将节省大量金钱。

# (17) 量化和验证(Quantifying and verifying)

这个作用体现于硬件设计流程中的实现(implementation)环节,主要是在PCB设计上。如果一个设计的简化工作做得好,那么验证将很容易。

验证主要依靠仿真工具。用仿真的方式验证 PCB 上走线是否合理。许多软件将 PCB 设计和仿真结合一起,为仿真结果反馈设计提供了方便。

在信号不完整的四种表现中,串挠必须在 PCB layout 后才能仿真,而反射则不一定,布线之前可以预定义一些电气约束规则,以此来驱动自动布线器或约束手工走线。

验证一条走线能否工作要看它的参数,如时间参数、波形边沿单调性和过冲等,对于33MHZ以上的工业产品,PCB走线要为信号留出足够的时间余裕。

(18) 当今的高速数字电路中,PCB 走线对信号的延迟已占了信号周期的相当部分,典型值是 1/3。

上图给出一个同步 PCB 上信号图,有三个部分周期图、原理图和电气表现图,一个周期包括从驱动器输出的时间, PCB 上传输时间、接收端建立时间,还有一个由于 CLK 到达驱动器和接收器时间不同而产生的时钟偏差(CLK slew)

电气图显示传输信号与时钟的时间差,图上标出了几个特征点,并以此得到out、prop、setup等时间参数,"out"的定义是对特定负载(这里是 OPF),驱动器输出达到某一电压时与时钟边沿的时间差。

参数 t\_prop 指驱动器发出信号到接收端得到稳定的信号。许多仿真器都能给出正确的结果。

建立时间和时钟偏差占了周期的剩余部分。

信号完整性工程师在这一阶段的任务是: 定量分析信号周期被 PCB 占用部分。

# (19) 设计和优化(Designing and optimizing)

这个作用体现于硬件设计流程的设计阶段。信号完整性工程师与项目组密切合作,提供有效建议,保证设计的高速部分在物理实现中能正常工作。

PCB 布线前就应该研究关键网络,针对这些网络,根据系统环境,研究 PCB 的走线方式。如果一时不能确定,那就要与项目组其他人讨论,以尽量找到办法。

设计阶段缺乏讨论交流往往导致系统性能下降甚至失败。

另一方面我们可以选择 I/O buffers 来满足物理的拓扑结构。设计者在选取驱动器时往往不能考虑到 PCB 的实际情况。如为了满足 IC 的要求会选取一个足够强的缓冲,实际中却因引入了太多噪声而破坏了系统时序。

优化 IC 的管脚可以缩短网络长度,对信号完整和减少 PCB 层次都有帮助, 优化还包括考虑电源地的数量和分布。

必须注意,一项设计不仅是 PCB 上如何走线,它是一个逻辑的、机械的和电气的元素的有机整体,项目组的每个人都要有"系统的概念"。

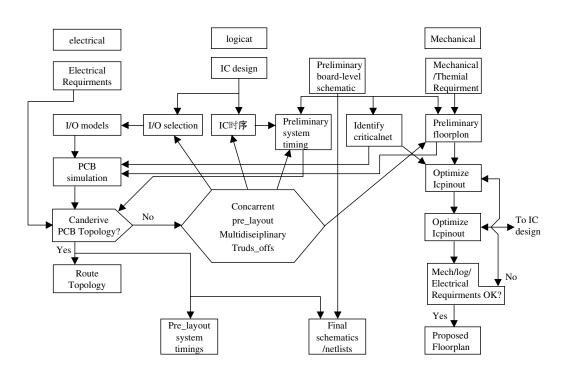

(20)

上图演示了得到 PCB 拓朴结构的详细过程,一个成功的信号完整性工程师应该知道怎样在大的系统设计中遵循这个过程前进。

工作的关键是利用已用的数据修正系统设计规则。(上图中间框内所示)一般来说,从系统的方面来调整设计是最容易的。

上图中关键的一步是"Route Topology",走线的结构合理能有效减少信号不完整方面的问题,保证又快又好地布线。工程师应在这方面尽较大努力。

产品设计必须考虑 I/O buffer、IC 时序、系统时序、IC 管脚、最终原理设计和实际板材(floorplan)各方面因素对一个有机体的影响,如果到产品实现(implementation)阶段才决定走线方式,那就失去了优化大系统环境的机会,而

得不到功能优良的产品。

- (21) 现在看个例子:如何针对一个固定的走线结构,优化缓冲器(buffer)因为结构限制,网络上 IC 的方向导致了一组总线布成 Y 形,引起特征阻抗不连续。如果加终端匹配或改变网络结构可能代价很高。现在看一下优化缓冲器的效果。

- (22) 含有这组地址总线的 ASIC 本身有九种不同的缓冲器可选 首先我们先算出每条线上的信号延迟时间

九种缓冲器要求设置(settle)延迟从 6ns 到 2ns。而缓冲器的饱和电流是从 30mA 到 250mA, 在一般 ASIC 终端中这意味着 2mA 到 24mA 的驱动能力。

#### (23) 现在选择缓冲器

如果系统时序允许 8ns 信号延迟, 1号 buffer 是首先目标。可是实际上 8ns 在高速电路中是很少见的。

首先,观察图的左半部分。在这边,驱动能力的提高大大减小了缓冲器设置 (settle)时间。缓冲器上网络的性能与缓冲器驱动能力很有关系,我们称这一区域为"buffer bound"。

相反,右半区称为"interconnect bounce"。缓冲器增强驱动能力并不能明显减小设置时间,但驱动能力强却能在传输线上得到较好效果。

现在,可见有五六种缓冲器可选。较弱的缓冲器对时间要求高,而强缓冲器又需要较多的给空间,并引入更多噪声。所均衡考虑取中间的缓冲器。

这个例子简单演示了信号完整性工程师在设计阶段可为其他设计者提供什么有价值的帮助。

# (24) 测量和建模 Measuring and Modeling

信号完整性分析中最困难的一步便是模型。一位经理认为具备有效精确的 IBIS 模型是成功进行信号完整性分析的第一要素。

在设计仿真之前,就必须有一个充分的模型库。这个任务是很难完成但必须完成。

有几种办法可得到模型。以网上下载或者仿真软件中也带了一些。越来越多的器件商开始提供这类模型,还有部分第三方模型供应商逐渐产生了。

可是如果你的设计中选了新器件,它的模型就不容易得到了,你有时就必须

自己建模。

当今的信号完整性工程师必须能熟练地建模。有时 SPICE 模型能转换成 IBIS 模型。有时就必须自己动手实测,条件好的话,最好用高精度的曲线跟踪仪器和示波器。条件不允许时较简单的仪器和测量方式也能奏效。

不管什么情况,都要尽力解决问题。争取用先进的工程方法、经验去得到最精确的数据,不要让项目停下来,说:我没有模型。

- (25) 数字 IC 的驱动器一般是从电源电压(逻辑"1")翻转到地电压(逻辑"0")。输出晶体管有着非线性的内阻,在 CMOS 工艺中,输出管中含有寄生二极管对信号翻转有影响。最常见的是 IC 驱动器还要经过某种封装才能与 PCB 相连接。

- (26) 当今的测试设备能精确测出这些器件的驱动特性。示波器便示测出器件驱动器的上下拉特性和嵌完特性,TDR(时域反射)系统能测出器件封装的寄生参数,这些数据足以建立 IBIS 模型。

# (27) 分类和总结 partition and Approximating

在硬件设计流程的研究(explore)阶段,信号完整性工程师需要有"分类和总结"能力。有时候虽然没有信号完整性工程师工作也能正常进行,但你必须考虑即将进行的设计中要的传输线结构和工作频率。

明确系统对带宽的要求。许多工程师迷恋于超出需求的宽带能力,这个阶段中,工程师又是要乐观的,在宣称"不可能"之前要仔细考虑,当你不确定时,做一些仿真工作,根据假设产生一些原始数据。

及时地将成果用于项目设计,不要太拘泥于细节拖延了时间。如果项目组其他人不理解你的话,你应给与充分说明,工程师应该热爱他的团队。

# (28) Pioneering and Defining 探索和定义

探索的大门永远是敞开的。永远有问题等待解决,提出新思想,仿真,实现,比较,最好的思想总是惊人的简单,从自然现象中提出来,揭示新的事物。

但就如已提到的那样,你必须与实际工作者充分合作。许多好思想深入不下去,就是因为提出者没能与他人很好的合作。

高速数字电路设计领域仍旧缺少很多建设性的工作。如果你有了好的想法,继续研究下去,你可能发现你的答案正准备应用于整个工业界。

# (29) PCI 总线设计例子:

信号完整性工程师在定义 PCI 总线的工作中起了很好的作用。1991 年底,设计一种高用的由 IC 直接驱动的总线的要求提出来了,新总线要能连接更多驱动器,速率比已有的高 4 倍。

通过许多前沿研究,我们能建立一种明确定义的仿真环境用于制造之前的仿真。系统仿真环境得到认可,PCI总线也因此得到优化。对驱动器的描述成为一种模型规范。反射波(Reflected\_wave)翻转(switching)成为一种解决自然现象的方法,实现了接插件(interconnect)直接由低功耗 ASIC 驱动的要求。

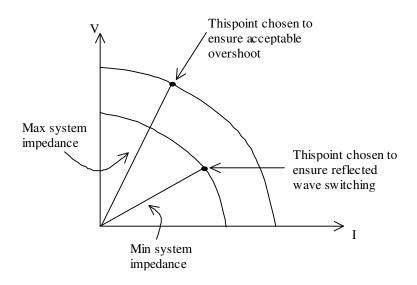

如图所示,如何利用系统条件(阻抗)和 IC 的特征曲线(V/I 曲线)去定义可靠的操作。这个过程可为任何接口定义一个设计空间。有了关键参数, IC 设计的灵活性便确定了。

(实际上,PCI 总线用另外的方法限定最大特性(Maximum characteristics), 而不是过冲。

### (30) 本文我们讨论了如何在当今高速数字电路中应用信号完整性工程

为保证信号完整,要求工程师认真分析数字设计的动态操作。这方面的工作还进行得很不够。信号完整性工程师的出现承担了这部分工作,他们应成为设计团队中的一部分,在整个硬件设计每一阶段中,信号完整性工程师体现了不同的作用,做出了贡献。如果信号完整性的工作效果良好,我们可大大提高产品性能,缩短上市时间,取得很好的经济效益。