#### Adapting Signal Integrity Tools and Techniques for 6 Gbps and Beyond

Donald Telian - SI Consultant

Session 8.3

### Agenda

- Why Serial Links?

- SI Moving Inside ICs

- Gbit Simulation Today

- Looking Forward

### Agenda

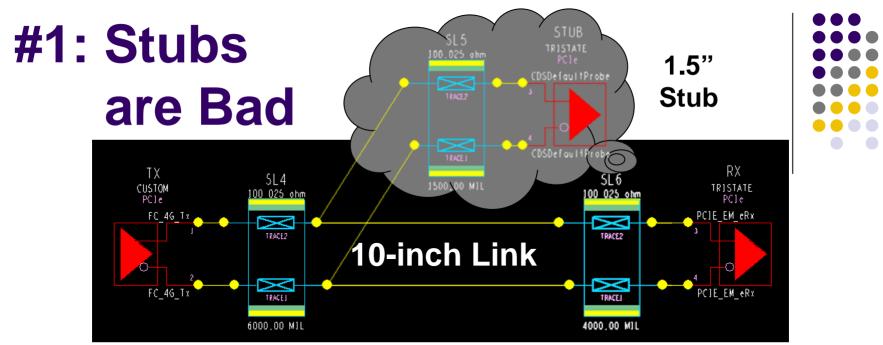

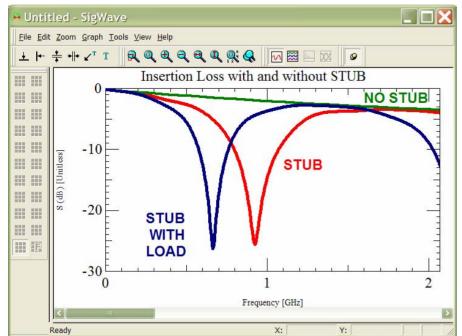

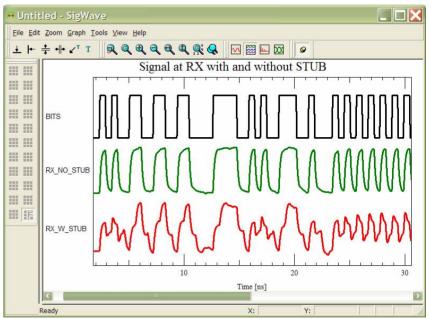

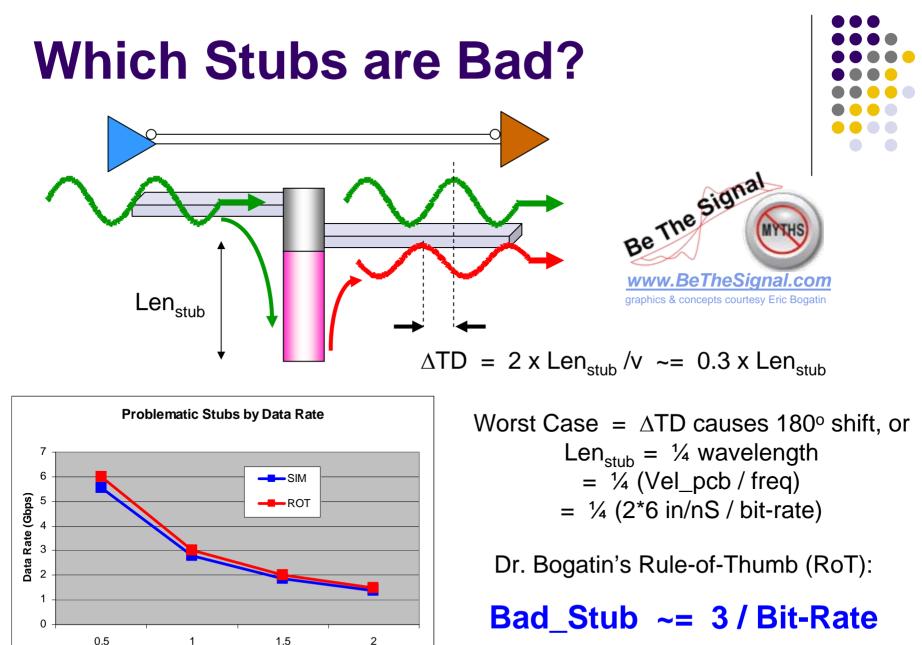

- Stubs are Bad

- Signals are Ugly

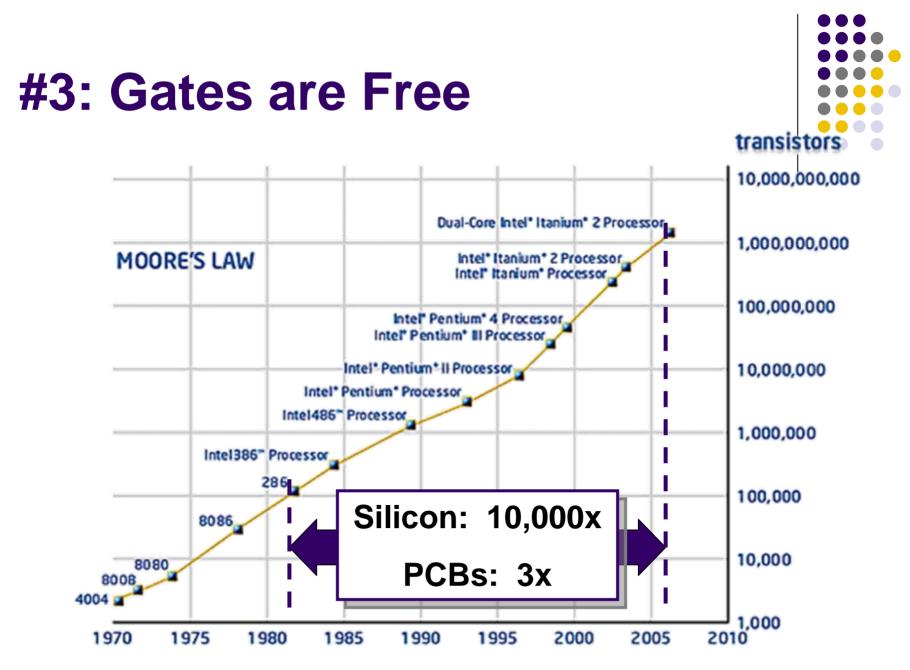

- Gates are Free

- SI Moving Inside ICs

- Gbit Simulation Today

- Looking Forward

Or, OK\_Stub ~= 3 / (10\*Bit-Rate) xxx\_Stub in inches, Bit-Rate in Gbps

Donald Telian SI Consultant

Stub Length (inches)

19

석카일

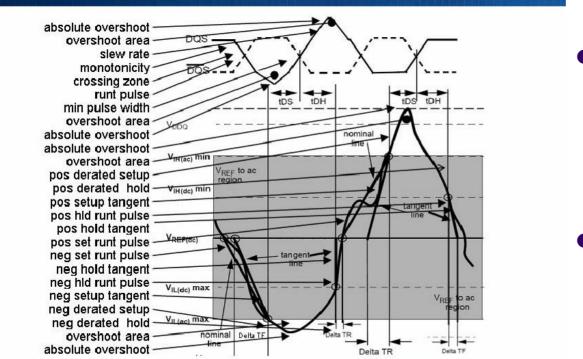

#### #2: Signals are Ugly

#### **Required DDR2 Measurements**

- High-speed signals need post-processing

- Shall we do that during design?

...or in silicon?

#### Receiver's behavior and specifications are sensitive to these effects

Micron

Source: "Single Simulation Analysis of a DDR2 Interface in IBIS 4.1" from DesignCon 2007, courtesy Randy Wolff, Micron Slide 6

#### **The Turning Point**

"We're now at the point where it's getting cheaper to put more gates behind a fast serial line than to lay down copper traces."

Jim Pappas, Intel

– commenting on why PCI Express used serial technology and PCI used parallel – EETimes February 18, 2002 page 92

#### Why Serial Links?

- Stubs are Bad

- Frequency issues arise with stubbed interconnects

- As early as 400 MHz, see <u>DesignCon 2006 Best Paper</u>

- The point-to-point nature of serial links removes stubs

- Signals are Ugly

- Receiving high-speed signals is challenging

- Serial links use built-in filtering to recover signals

- Gates are Free

- Surplus silicon has added features to IO transceivers

- Signal Integrity is moving inside the chip

### Agenda

- Why Serial Links?

- SI Moving Inside ICs

- Transmitters (Tx)

- Receivers (Rx)

- Gbit Simulation Today

- Looking Forward

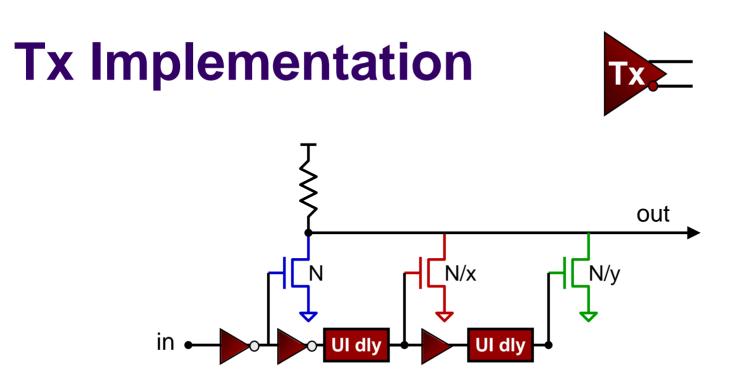

#### **Tx Techniques**

- Adapting signal at Tx is simpler than Rx

- Data pattern is known

- Around 2.5 Gbps "pre-emphasis" was used

- Sometimes called "de-emphasis" or "2-taps"

- At higher rates, more "taps" are used

- Some taps before bit, or "pre-cursor"

- Taps typically spaced by bit times

- Most efficient when Rx signal understood

- Through simulation, spec boundaries, etc.

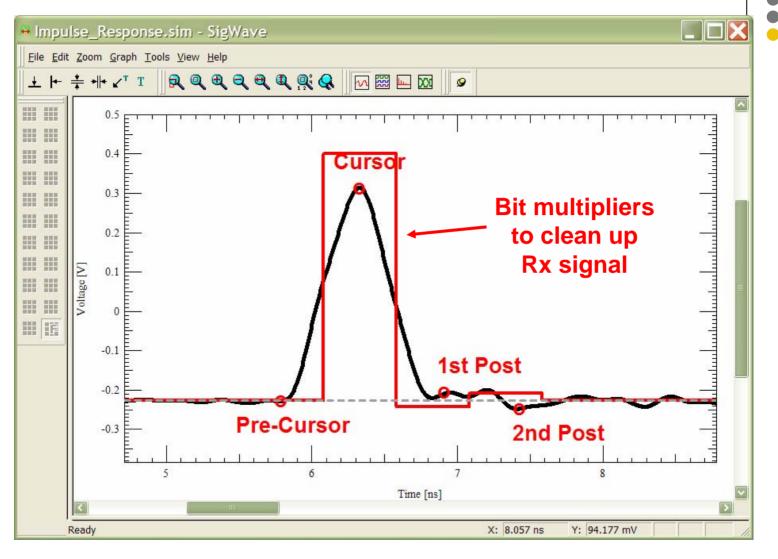

#### **Taps & Impulse Response**

Slide 12

- Bit-stream fed directly to SerDes

- For more detail, see Cadence webinar

- How to build fast and accurate multi-gigabit transceiver models

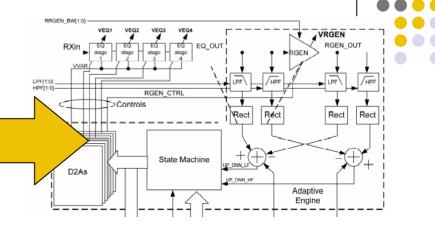

#### **Rx Techniques**

- Rx Equalization (EQ) is more challenging

- Data pattern is NOT known

- Signal at Rx has often disappeared

- typically 20 dB down (10% of signal) at 6+ Gbps

- Primary area of SerDes advances

- Higher speeds = more creative solutions

- Techniques increasingly complex and/or non-linear

- DFE = Decision Feedback Equalization

- Some are continuously adaptive

- Implementations inconsistent

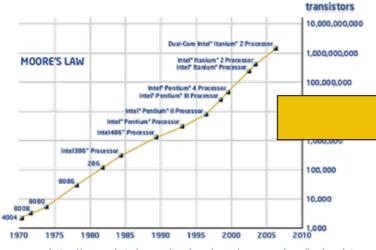

#### **Moore's Law Meets IO Interfacing**

source: http://www.intel.com/technology/mooreslaw/index.htm

source: DesignCon 2007 Paper "Digitally Assisted Adaptive Equalizer in 90 nm With Wide Range Support From 2.5 Gbps to 6.5 Gbps" see <u>http://www.altera.com/literature/cp/cp-01026.pdf</u>

#### An increasing amount of transistors are consumed by signal transmission

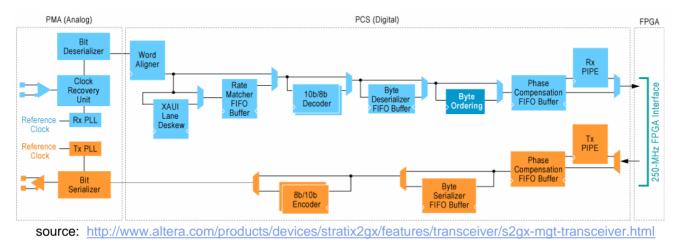

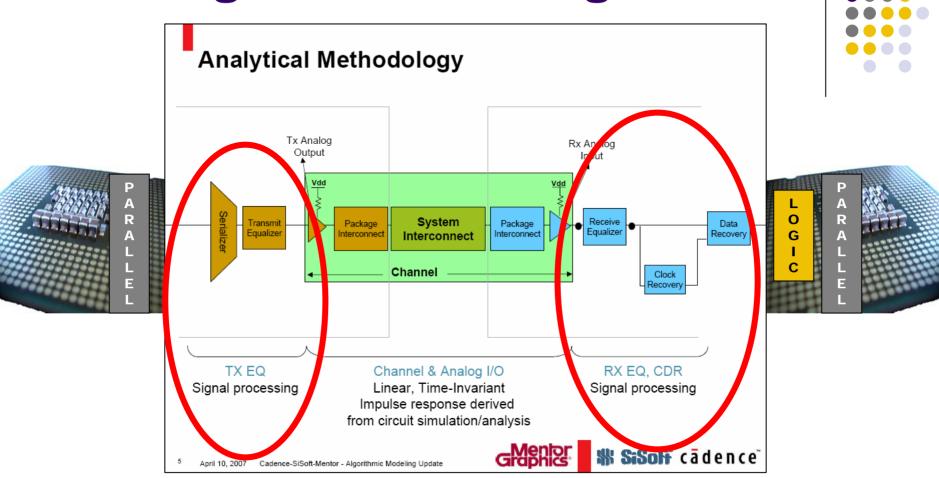

#### **IO = Signal Processing?!**

Source: http://www.vhdl.org/pub/ibis/macromodel\_wip/archive/20070410/toddwesterhoff/Algorithmic%20Modeling%20BIRD%20-%20Update/IBIS-ATM\_Apr10-v3.pdf

There's a lot of gates between serial and parallel

Communications theory has met the digital IO

### Agenda

- Why Serial Links?

- SI Moving Inside ICs

- Gbit Simulation Today

- Outside the IC

- Inside the IC

- Signal Processing

- Looking Forward

### Outside the IC = S-Parameters

#### • S-params common for passive interconnect

- Lab characterization covered for absence of tools

- Generated by both measurement and analysis tools

- Viewed as better than cascaded discrete models

- Can read loss directly from S-param plots

- Format for industry-standard "channels"

- Now handled by most PCB analysis tools

- Some more mature than others

- Proper fixturing/measurement is challenging

- For more details see Cadence webinar

- Understanding and Using S-Parameters for PCB Signal Integrity

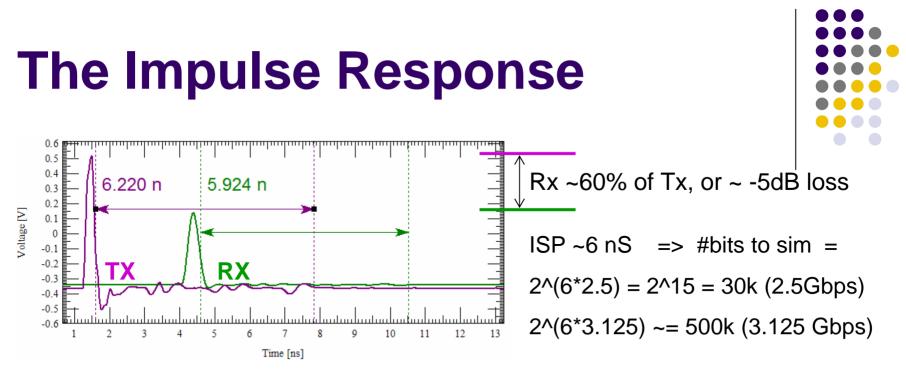

- System interconnect's "fingerprint"

- Reveals Tx to Rx "loss" (similar to eye or S\_21)

- Reveals "Interconnect Storage Potential (ISP)"

- From which we can determine # bits to simulate

- ISP detailed in Intel/Cadence DesignCon 2005 paper <u>"New Techniques for Designing and Analyzing Serial Links"</u>

- Used in <u>"high-capacity" simulators</u>

### **Understanding Analog Tx/Rx**

- The simple IO had a set of characteristics

VI, T rf (VT), C comp

- And the differential Tx and Rx do too

- V\_swing, T\_rf, V\_cm, R\_term, Pre-emp%, Cpad

- Same Tx/Rx handles multiple standards

- Excessively programmable

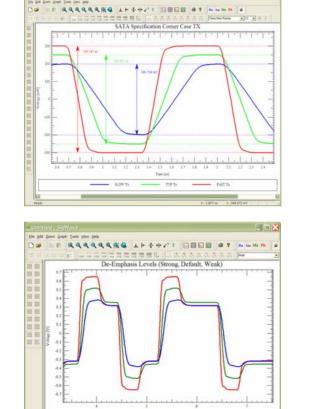

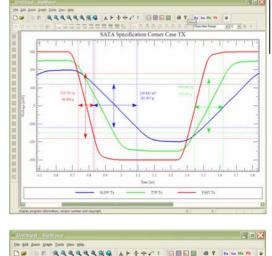

#### **Using "Spec" Models**

SATA Spec Voltage Swing & Edge Rates

~PCI Express Voltage Swing & Edge Rates

- <u>Craft</u> from base set of parameters in Specs

- Set of model templates at this link

### Beyond Analog Tx/Rx ~ Modeling Signal Processing

- Tools and models exist within IC companies

- Used for IC architecture and design

- Excessively proprietary

- In some cases they're offered to customers

- Support issues

- Maintenance issues

- THE BIG ISSUE

- Require same IC (vendor) on both ends of the link

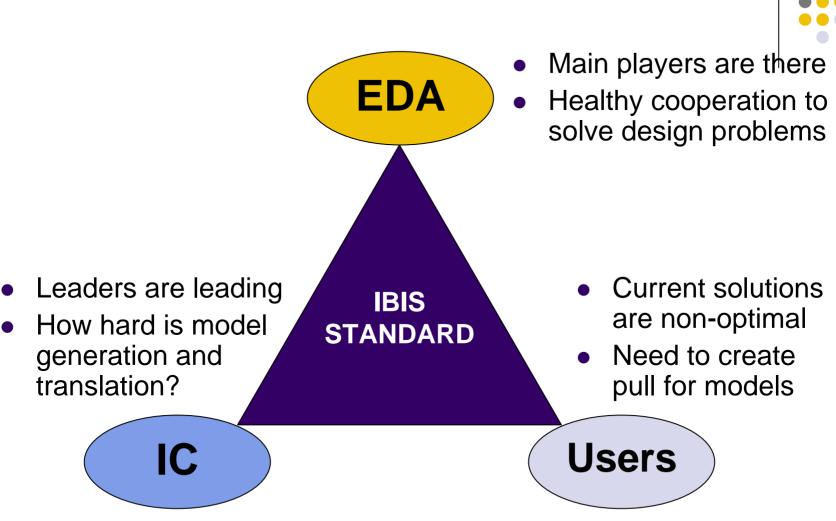

#### **Interoperability Challenge**

- Must simulate models from different vendors

- It happened once before with "IBIS"

- Early '90s many IBIS-like SI simulators emerged

- Plug n Play SI required consistent model format

- IBIS was born

- Once again the leaders are deriving a format

- Executable "Algorithmic Models" contained in DLLs

- All work in public domain done by IBIS-ATM

IBIS Advanced Technology Modeling Task Group

### Agenda

- Why Serial Links?

- SI Moving Inside ICs

- Gbit Simulation Today

- Looking Forward

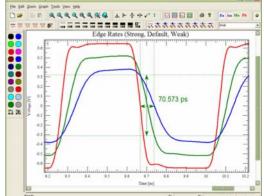

#### **Towards Interoperability**

#### **IBIS-ATM SerDes Task Group**

- Goal: SerDes Rx/TX model interoperability

- Multiple EDA platforms

- Multiple SerDes vendor models

- Protect SerDes vendor IP

- IBIS-ATM committee participation

- EDA: Agilent, Cadence, Mentor, SiSoft

- Semiconductor: IBM, Intel, Micron, ST-Micro, TI, Xilinx

- System: Cisco

- Two part modeling standard

- Characterization model: existing IBIS syntax models TX / RX analog characteristics

- Algorithmic model: equalization, clock recovery, device optimization algorithms

Slide courtesy IBIS-ATM Group and Todd Westerhoff: <u>http://www.vhdl.org/pub/ibis/summits/sep07/</u>

• IBIS-ATM: <a href="http://www.vhdl.org/pub/ibis/macromodel\_wip/">http://www.vhdl.org/pub/ibis/macromodel\_wip/</a>

Algorithmic models typically implemented in .dll files

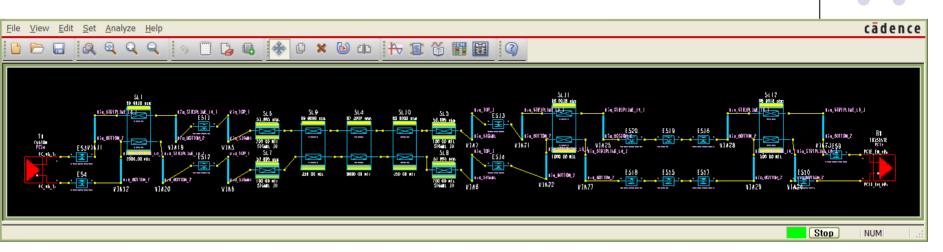

#### Algorithmic Models Within Cadence Flow

cādence

- Algorithmic models fit within existing MGH flow

- Invoked as part of Channel Analysis, some scripts etc.

- Cadence demo'd in Jan07, released in 16.0

- Tx/Rx macromodels contain "ami" portion

- Includes path to dll file and settable parameters

- Cadence working towards industry standardization

- Within IBIS domain (proprietary solution for now)

#### **Industry Standardization**

#### **IBIS-ATM Status**

Original proposal submitted by Cadence & IBM Current version authored by Cadence, Mentor, SiSoft First draft of BIRD approved by IBIS-ATM task group for prototype model & EDA platform development Prove interoperability & refine proposal before bringing back to IBIS Open Forum Subcommittee work, presentations & BIRD available on-line: http://www.vhdl.org/pub/ibis/macromodel\_wip/ Public TX/RX models, modeling "toolkits" will be available

Status courtesy IBIS-ATM Group and Todd Westerhoff: http://www.vhdl.org/pub/ibis/summits/sep07/

- Achieved model/EDA interoperability in Aug 2007

- Updated proposal (BIRD) for ATM approval ~Sep/Oct 2007

- ...and then on to IBIS committee approval and release

#### **SerDes SI into Mainstream**

Pieces are coming into place to enable push past 6 Gbps

#### **Existing Solutions**

- IBM offers Algorithmic Models for their 6 Gbps and 11 Gbps SerDes NOW

- Operates within Allegro PCB SI 16.0

- Available only to IBM customers

- Contact your local IBM representative to obtain models

- IBIS-ATM group released AMI model Eval Toolkits

- Visit the Work Archive at: <u>http://www.vhdl.org/pub/ibis/macromodel\_wip/</u>

#### In Summary

- Serial links dominate for higher speeds

- Signal integrity moving inside chips

- Models, methods, metrics changing

- SerDes now do signal processing

- Interoperable models an issue

- Cadence/others driving a solution

- Algorithmic models coming into place

## THANK YOU

cadence designer network

# CONNECT: IDEAS

#### **CDNLive! 2007 Silicon Valley**